4.4. COMPUERTA NOR DE 3 ENTRADAS

4.4.1. CIRCUITO ELECTRICO

Una compuerta NOR de 3 entradas se puede describir mediante el circuito eléctrico de la figura 4.34

Para analizar el circuito partimos de que el interruptor abierto es un BAJO (“0” lógico) y que el interruptor cerrado es un ALTO (“1” lógico). Lámpara apagada es un BAJO (“0” lógico) y lámpara encendida es un ALTO (“1” lógico).

Se puede deducir que la lámpara enciende (“1” lógico) cuando los tres interruptores está abiertos (“0” lógico). Con cualquier interruptor que esté cerrado (“1” lógico) la lámpara no encenderá (“0” lógico).

Figura 4.34 Compuerta NOR de 3 entradas con componentes eléctricos

4.4.2. COMPUERTA NOR DE 3 ENTRADAS A TRANSISTORES

Un circuito electrónico con transistores bipolares que cumple a cabalidad con la implementación de una compuerta NOR de 3 entradas se muestra en la figura 4.55

Al tener 3 entradas una compuerta, se

presentan 8 posibles combinaciones entre sus entradas la cual detallaremos en

su tabla de verdad.

Figura 4.35 Compuerta NOR de 3 entradas con transistores

4.4.3. OSCILOGRAMAS DE LA COMPUERTA OR DE 3 ENTRADAS

En la figura 4.36. se han dibujado los niveles aplicados a las entradas A, B y C, y el obtenido a la salida Y de un circuito lógico, como la que se ha dibujado en la figura 4.35

Entre 0 y 50ns, se aplican los niveles de voltaje: A = BAJO, B = BAJO y C = BAJO. Obteniéndose a la salida, Y = ALTO.

Entre 50 y 100ns, se aplican los niveles de voltaje: A = ALTO, B = BAJO y C = BAJO. Obteniéndose a la salida, Y = BAJO.

Entre 100 y 150ns, se aplican los niveles de voltaje: A = BAJO, B = ALTO y C = BAJO. Obteniéndose a la salida, Y = BAJO.

Entre 150 y 200ns, se aplican los niveles de voltaje: A = ALTO, B = ALTO y C = BAJO. Obteniéndose a la salida, Y = BAJO.

Entre 200 y 250ns, se aplican los niveles de voltaje: A = BAJO, B = BAJO y C = ALTO. Obteniéndose a la salida, Y = BAJO.

Entre 250 y 300ns, se aplican los niveles de voltaje: A = ALTO, B = BAJO y C = ALTO. Obteniéndose a la salida, Y = BAJO.

Entre 300 y 350ns, se aplican los niveles de voltaje: A = BAJO, B = ALTO y C = ALTO. Obteniéndose a la salida, Y = BAJO.

Entre 350 y 400ns, se aplican los niveles de voltaje: A = ALTO, B = ALTO y C = ALTO. Obteniéndose a la salida, Y = BAJO.

Figura 4.36 Oscilograma de la compuerta NOR de 3 entradas

4.4.4. SÍMBOLO DE LA COMPUERTA NOR DE 3 ENTRADAS

El símbolo de la compuerta NOR de 3

entradas viene representado en la figura 4.37.

Figura 4.37 Símbolo de la compuerta NOR de 3 entradas

4.4.5. TABLA DE VERDAD DE LA COMPUERTA NOR DE 3 ENTRADAS

En primer lugar, y como ya se habrá observado, la tabla de verdad de la compuerta NOR de 3 entradas debe contener un total de ocho filas, correspondientes a los ocho casos posibles descritos en la sección 4.4.3, por medio de los cuales se puede llegar de modo diferente a la obtención del valor del nivel de la salida

|

Entradas |

Salida |

||

|

C |

B |

A |

Y |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

Figura 4.38 Tabla de verdad de la compuerta NOR de 3 entradas

La tabla de verdad nos muestra que con cualquier “1” que exista en una de sus entradas , habrá un “0” en la salida.

4.4.6. FÓRMULA DE LA COMPUERTA NOR DE 3 ENTRADAS

De la tabla de verdad de la figura 4.38, se ve claramente que se puede aplicar la inversión de la operación suma inclusiva a todas las líneas de la tabla, por lo que diremos que la fórmula de esta función NO-O es, para lógica positiva:

Y = (C + B + A)'

4.4.7. COMPUERTA NOR DE 3 ENTRADAS CON CIRCUITOS INTEGRADOS

En este apartado se describirán los circuitos integrados que contienen compuertas lógicas NOR de 3 entradas.

4.4.7.1. CIRCUITO INTEGRADO TTL 74LS27

En la figura 4.39 podemos apreciar una cápsula del tipo DIL 14, es decir, que tiene 14 pines y que en su interior tiene integradas tres compuertas NOR de tres entradas cada una. Estas compuertas son similares a las descritas, transistorizadas, en la figura 4.35.

Los 0 voltios (GND), de todos los circuitos se proporcionan a través del pin 7, mientras que los 5 voltios (VCC) se conectan al pin 14. Las entradas de las tres compuertas AND son: 1, 2 y 13; 3 , 4 y 5; 9, 10 y 11, y las salidas respectivas: 12, 6 y 8.

Figura 4.39 Distribución de pines del circuito integrado 74LS27

La figura 4.40 muestra la

simulación de la compuerta NOR de 3 entradas TTL en el software PROTEUS 8.13.

Figura 4.40. Circuito TTL para comprobar la compuerta NOR de 3 entradas

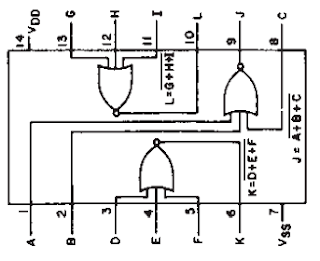

4.4.7.2. CIRCUITO INTEGRADO CMOS 4025

La figura 4.41 muestra el pinout del circuito integrado CMOS 4025

Los 0 voltios (GND), de todos los circuitos se proporcionan a través del pin 7, mientras que los 15 voltios (VDD) se conectan al pin 14. Las entradas de las tres compuertas NOR son: 1, 2 y 8; 3 , 4 y 5; 11, 12 y 13, y las salidas respectivas: 9, 6 y 10.

Figura 4.41 Distribución de pines del circuito integrado 4075

La figura 4.42 muestra la

simulación de la compuerta NOR de 3 entradas CMOS en el software PROTEUS 8.13.

Figura 4.42. Circuito CMOS para comprobar la compuerta NOR de 3 entradas

4.4.8. IMPLEMENTACIÓN DE UNA COMPUERTA NOR DE 3 ENTRADAS CON COMPUERTAS NOR DE 2 ENTRADAS

En algunas ocasiones no se encuentran en el comercio circuitos integrados con compuertas lógicas de más de dos entradas. Se hace entonces necesario implementar las compuertas de tres entradas colocando compuertas de dos entradas en serie, tal como se muestra en la figura 4.43

Figura 4.43. Compuerta NOR de 3 entradas implementada con compuertas NOR de 2 entradas

El análisis de este circuito lo podemos

realizar mediante una tabla de verdad. Se realiza primero la salida parcial

entre las entradas C y B; luego se realiza la inversión de la salida (C + B)' y finalmente la salida total entre la salida parcial ((C + B)')' y la entrada A.

Se puede apreciar que la salida total Y es idéntica a la de la tabla de verdad de la figura 4.38

|

Entradas |

|

Salidas |

|||

|

C |

B |

A |

(C + B)' |

((C + B)')' |

Y |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

Figura 4.44 Tabla de verdad de la figura 4.43

4.4.9. MONTAJE EN PROTOBOARD DE UNA COMPUERTA NOR

Figura 4.45. Compuerta Nor de 3

entradas en Protoboard

No hay comentarios.:

Publicar un comentario